双面板上的USB2.0

二层板设计高速数字信号线,无外乎两个原则,一是走线要尽量短,长度小于信号波长的十分之一

二是无法短的,就控制它的阻抗。

我们先来确定电路板的参数:

1.6mm电路板,1oz(盎司)铜箔,介质FR4,介电常数4.6~4.8,板芯厚度1.5mm。

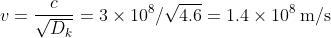

按照这些数据我们来计算电路板上信号传播的速度。其中Dk为介电常数

也就是说每个纳秒能传播的距离是14cm。

接下来计算在双面板上可以布多长的走线而不需要考虑阻抗匹配的问题

USB2.0有三种速度模式:

1.低速模式:传输速率1.5Mbps

2.全速模式:传输速率12Mbps

3.高速模式:传输速率480Mbps

在低速模式下:

上升沿时间一般为75~300ns

在高速数字电路设计中,临界长度的定义通常与信号在传输线上的时延有关,而10% 的标准通常用于评估信号在传输线上引起显著反射的可能性。当信号传输路径的长度达到信号上升时间(或下降时间)的10%时,传输线效应(如反射、阻抗失配等)可能会开始对信号质量产生明显的影响。这个10% 是经验值,表示在这个范围内,信号可能已经在传输线上出现了足够的延迟,导致反射影响开始变得明显。

临界长度(10%):(14cm/ns*75ns)/10 = 1m

所以在低速模式下,可以当做普通布线随便走线,无需特别处理

在全速模式下:

上升沿时间一般为4~20ns

临界长度(10%):(14cm/ns*4ns)/10 = 5.6cm

临界长度(25%):(14cm/ns*4ns)/4 = 14cm

在全速模式应用中,只要走线不是特别长,不会到要按照传输线进行阻抗匹配的地步,况且大多数USB控制器对超出规格的信号有很好的容忍度

在高速模式下:

上升沿时间一般为500ps

临界长度(10%):(14cm/ns*500ps)/10 = 7mm

临界长度(25%):(14cm/ns*500ps)/4 = 17.5mm

这时候控制PCB走线的阻抗就十分重要了,即使是很短的走线也开始接近信号的波长了。

按照USB2.0的技术标准数据线D+和D-是一对差分信号线,差分阻抗为90欧。

差分对长度匹配的条件,USB2.0给出的要求是,允许两条数据线之间可以有100ps的时钟偏移,换算成走线长度就是两条差分信号线长度偏差是1.4厘米。下一步就是根据这些参数计算实际PCB走线的宽度和间隔要求。

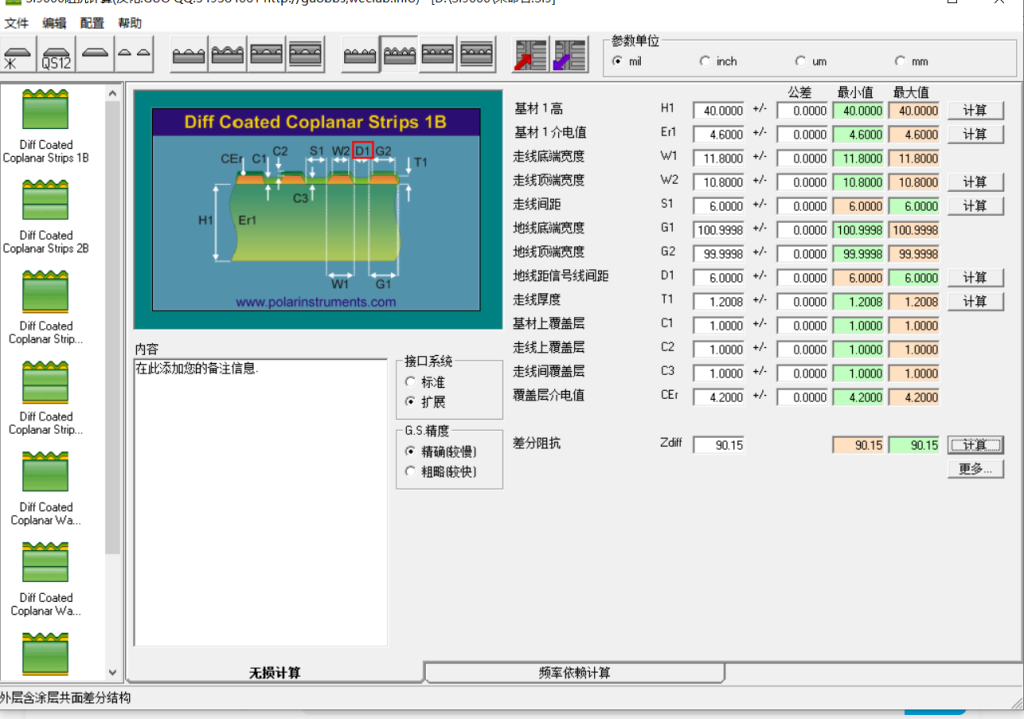

如果板上空间足够,可以在差分线两侧加上接地线,这样可以在板芯厚40mils,宽11mils,间距6mils,两侧接地,地宽100mils的情况下获得90欧的差分阻抗